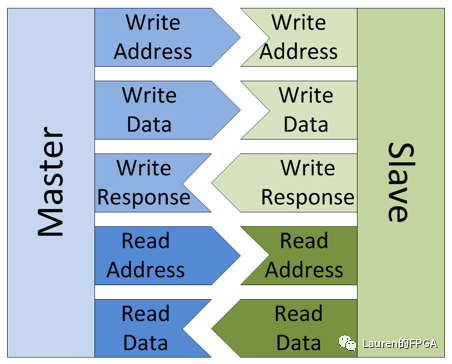

AXI-4 Memory Mapped也被稱之為AXI-4 Full,它是AXI4接口協議的基礎,其他AXI4接口是該接口的變形。總體而言,AXI-4 Memory Mapped由五個通道構成,如下圖所示:寫地址通道、寫數據通道、寫響應通道、讀地址通道和讀數據通道。

上圖中的箭頭方向表明了信號的流向(主到從或從到主)。例如:對于寫通道,主設備把數據發送給從設備,同時從設備給主設備發送響應信號,表明數據交易的完成。對于讀通道,從設備根據主設備提供的地址信息把數據發送給主設備。

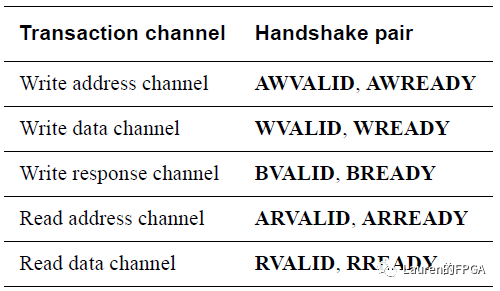

每個通道都有自己的VALID/READY握手信號對,如下圖所示。只有當握手信號同時有效時,該通道其他信號才有效。

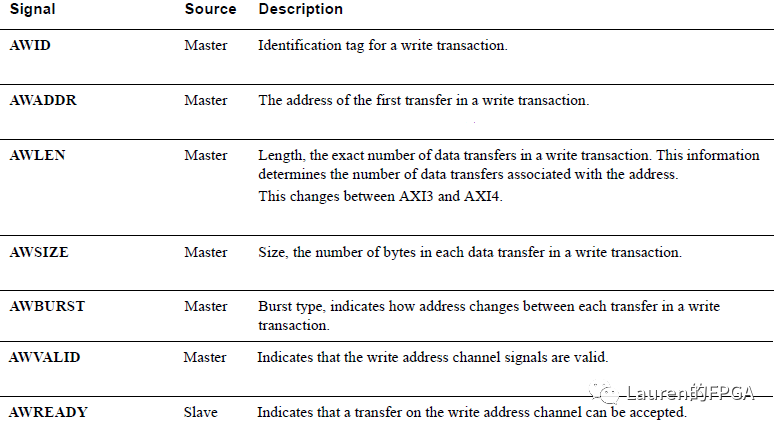

寫地址通道

對于寫地址通道,這里主要介紹以下幾個信號,如下圖所示。寫地址通道的信號名稱均以AW開頭。從圖中可以看到除AWREADY之外,其余信號均由主設備產生傳遞給從設備。AWADDR為寫數據第一個Byte的地址,從設備會根據此值計算后續Byte地址。AWLEN+1即為突發長度,表明了發送數據的個數(不是Byte數)。

-

接口協議

+關注

關注

5文章

41瀏覽量

18597 -

AXI4

+關注

關注

0文章

20瀏覽量

8915

原文標題:深入理解AXI-4 Memory Mapped 接口協議

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何使用AXI VIP在AXI4(Full)主接口中執行驗證和查找錯誤

看看在SpinalHDL中AXI4總線互聯IP的設計

SoC Designer AXI4協議包的用戶指南

AMBA 4 AXI4、AXI4-Lite和AXI4-流協議斷言用戶指南

何謂 AXI?關于AXI3/AXI4的相關基礎知識

AXI3與AXI4寫響應的依賴區別?

漫談AMBA總線-AXI4協議的基本介紹

SoC設計中總線協議AXI4與AXI3的主要區別詳解

Xilinx NVMe AXI4主機控制器,AXI4接口高性能版本介紹

AMBA AXI4接口協議概述

AXI4接口協議的基礎知識

AXI4接口協議的基礎知識

評論