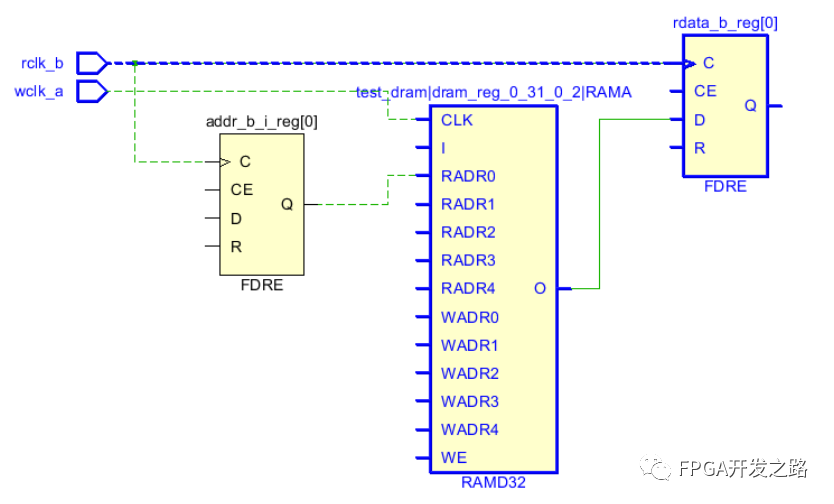

當(dāng) LUTRAM 讀寫使用不同的時鐘,寫時鐘 wclk_a,讀時鐘 rclk_b。

總結(jié)

When the read and write addresses are different, there is no CDC path between the write and the read clocks.

However, when the write and read addresses are the same, then there is a CDC path between the write clock and the read clock.

原因

當(dāng)讀寫地址不同時,讀數(shù)據(jù)時數(shù)據(jù)不會發(fā)生寫入,和寫時鐘無關(guān),讀出數(shù)據(jù)的delay是固定的,因此從 讀地址寄存器到 輸出寄存器 是一條同步路徑。

當(dāng)讀寫地址相同時,讀數(shù)據(jù)時該地址同時正在被寫入,讀出數(shù)據(jù)的delay的是依賴于寫時鐘的,如果讀寫時鐘靠的很近,輸出寄存器就可能出現(xiàn)亞穩(wěn)態(tài)。從 LUTRAM 到 輸出寄存器 是一條異步路徑。

Reference:

《Vivado Design Suite User Guide: Design Analysis and Closure Techniques》

-

寄存器

+關(guān)注

關(guān)注

31文章

5363瀏覽量

121169 -

數(shù)據(jù)

+關(guān)注

關(guān)注

8文章

7139瀏覽量

89579 -

時鐘

+關(guān)注

關(guān)注

11文章

1747瀏覽量

131802

原文標(biāo)題:LUTRAM 讀寫使用不同時鐘的 CDC Path

文章出處:【微信號:FPGA開發(fā)之路,微信公眾號:FPGA開發(fā)之路】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

FPGA User Guide之report_cdc

USB兩個COM的讀寫速率基本保持一樣,如果同時測試讀寫速率會受影響嗎?

請問當(dāng)CLB配置為SRL或LUTRAM時,SRL或LUTRAM在Virtex-5中使用的幀號是多少?

如果同時要開發(fā)esp32和esp8266該怎樣設(shè)置PATH和IDF_PATH?

基于FALSE PATH的設(shè)置

ic設(shè)計(jì)——CDC的基本概念

vivado多時鐘周期約束set_multicycle_path使用

ASIC/FPGA設(shè)計(jì)中的CDC問題分析

XDC約束技巧之CDC篇

CDC341時鐘驅(qū)動器數(shù)據(jù)表

具有三態(tài)輸出的CDC339時鐘驅(qū)動器數(shù)據(jù)表

CDC2510C鎖相環(huán)時鐘驅(qū)動器數(shù)據(jù)表

CDC2351高性能時鐘驅(qū)動器電路數(shù)據(jù)表

LUTRAM 讀寫使用不同時鐘的CDC Path

LUTRAM 讀寫使用不同時鐘的CDC Path

評論