多晶硅柵的形成是集成電路工藝中最關(guān)鍵的步驟,因?yàn)樗俗畋〉臇叛趸瘜拥臒嵘L(干氧和濕氧),形成多晶硅柵的先進(jìn)且復(fù)雜的光刻技術(shù)和干法刻蝕技術(shù),以及需要精確控制且復(fù)雜的側(cè)墻工藝。

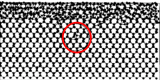

多晶硅柵結(jié)構(gòu)通常是一代集成電路工藝中物理尺度最小的結(jié)構(gòu),也是形成晶體管的關(guān)鍵。多晶硅柵形成的一般流程是,首先使用高溫?zé)嵫趸蓶叛趸ぃさ暮穸燃s為 1~10nm(由于在集成電路中有不同工作電壓的場效應(yīng)晶體管,所以柵氧化層的厚度也不相同,需要采取多個步驟才能完成不同厚度的柵氧化層),然后進(jìn)行多晶硅柵的化學(xué)氣相沉積和摻雜(擴(kuò)散或離子注入),最后進(jìn)行光刻和干法刻蝕。

多晶硅柵光刻工藝使用的光刻機(jī)是同一技術(shù)代集成電路工藝線中最先進(jìn)、最昂貴的設(shè)備,它采用 UV 光源進(jìn)行曝光,波長從g線(436nm)到DUV(248pm 和 193nm),以及 193nm 浸沒式;在光刻掩模版上采用了 OPC和PSM等技術(shù);在光刻工藝中采用了抗反射層、硬光刻膠技術(shù)、多重曝光技術(shù)等。

多晶硅柵的刻蝕采用的是最精細(xì)的刻蝕設(shè)備和技術(shù),通常采用 NF3、 SF6~HBr、CL2,等氣體,要求與 SiO2有極高的選擇比。多晶硅柵的檢測技術(shù)也是最精細(xì)的檢測技術(shù),用于光刻和刻蝕完成后多晶硅柵線寬和形狀等的檢測。

雖然在 45nm 以下的超大規(guī)模集成電路制造工藝中,為了解決多晶硅柵耗盡效應(yīng),以及多晶硅與高K介質(zhì)高界面態(tài)密度等問題,多采用了高K金屬柵工藝,多晶硅柵的重要性有所降低,但是多晶硅柵工藝仍然被認(rèn)為是集成電路的標(biāo)志性工藝之一。

審核編輯 :李倩

-

集成電路

+關(guān)注

關(guān)注

5392文章

11624瀏覽量

363201 -

多晶硅

+關(guān)注

關(guān)注

3文章

241瀏覽量

29384

原文標(biāo)題:多晶硅柵(Poly-Si Gate)

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

Poly-SE選擇性多晶硅鈍化觸點(diǎn)在n-TOPCon電池中的應(yīng)用

多晶硅的存儲條件是什么

今日看點(diǎn)丨美國宣布提高中國太陽能硅片、多晶硅關(guān)稅50%;聯(lián)發(fā)科天璣 8400 芯片詳細(xì)參數(shù)曝光

效率提升0.15-0.2%:雙面Poly和Poly Finger技術(shù)在TOPCon電池中的創(chuàng)新應(yīng)用

多晶硅生產(chǎn)過程中硅芯的作用

多晶硅柵工藝的制造流程

光伏多晶硅的應(yīng)用領(lǐng)域有哪些

光伏多晶硅的分片方法及優(yōu)缺點(diǎn)

Poly層厚度對N型TOPCon太陽能電池電學(xué)性能的影響

多晶硅柵耗盡效應(yīng)簡述

大全能源半導(dǎo)體級多晶硅項(xiàng)目首批產(chǎn)品成功產(chǎn)出

控制多晶硅(poly-Si)/4H-SiC異質(zhì)結(jié)二極管能壘高度(ΦB)的方法

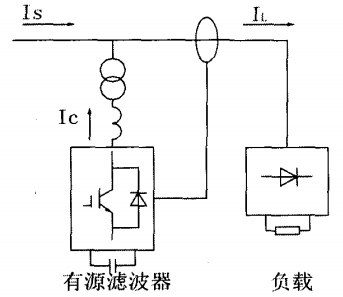

淺談安科瑞有源濾波器在多晶硅行業(yè)中的應(yīng)用

多晶硅柵(Poly-Si Gate)

多晶硅柵(Poly-Si Gate)

評論