在PCB設計過程中,一把布線的順序是先走信號線,然后進行電源的處理、電源的分割,然而電源的飛線是非常多的,非常影響信號線的布線,所以剛開始會將電源的飛線進行隱藏,具體操作的步驟如下所示:

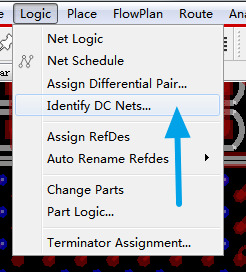

1.點擊執行菜單命令Logic-Identify DC Nets,如圖1所示,定義電源的電壓屬性;

圖1 定義電壓屬性示意圖

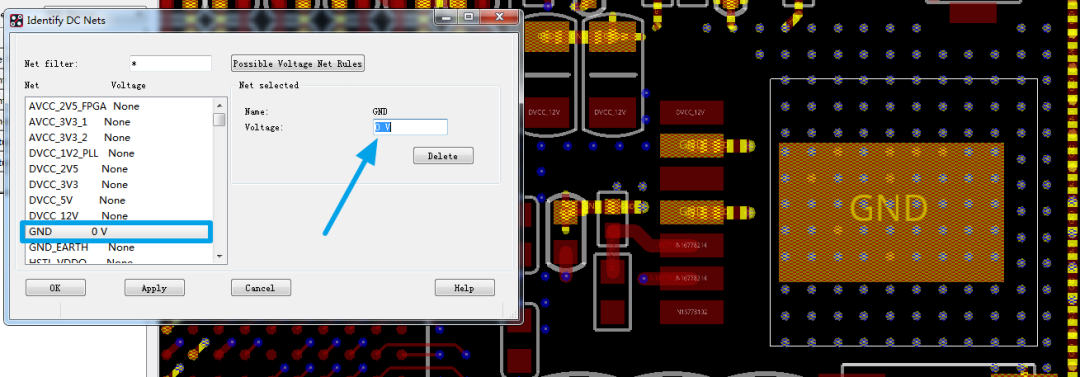

2.進入電壓設置界面,可以從網絡列表選擇網絡,也可以是鼠標去PCB界面進行點擊,如圖2所示,我們選擇到GND網絡,目前是沒有賦予電壓值的,顯示是None,在Voltage欄輸入電壓值為0,這樣飛線就會收起來了;

圖2將電源飛線收起示意圖

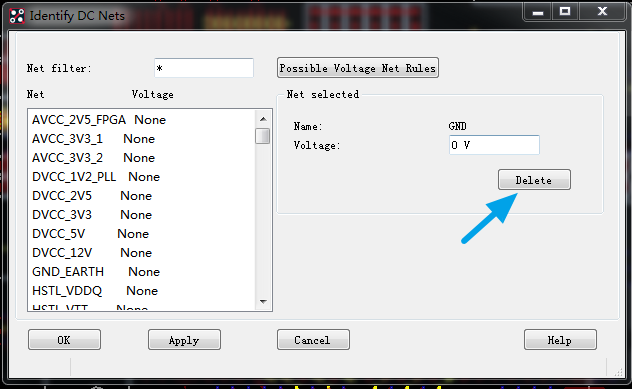

3.如圖3所示,將電壓值指定好以后,點擊Apply命令運用下,飛線就收起來,不會到處飛,方便對其它信號線的布線以及規劃。其它電源的飛線,跟這個的處理方法是一致的,也是賦予電壓值即可,是多少伏特的電壓值就賦予多少電壓值即可。

上述,就是在Allegro軟件中,對電源飛線進行隱藏的方法解析,當信號線布完之后,需要顯示電源的飛線,將之前的賦予的電壓值進行刪除即可。

圖3 地網絡飛線收起示意圖

嘉立創EDA專業版PCB絲印的快速調整方法

嘉立創EDA專業版尺寸標注操作教程

嘉立創EDA專業版PCB距離測量操作

嘉立創EDA PCB設計對齊與等間距操作

嘉立創EDA PCB設計移動操作命令介紹

點擊“閱讀原文”查看更多干貨文章

原文標題:?Cadence Allegro飛線的隱藏關閉

文章出處:【微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

-

pcb

+關注

關注

4326文章

23161瀏覽量

399989

原文標題:?Cadence Allegro飛線的隱藏關閉

文章出處:【微信號:FANYPCB,微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Cadence官方出品CadencePCBViewers

如何解決老舊小區“飛線充電”,減少火災事故

cadence allegro orcad各版本軟件下載鏈接分享

淺談社區“飛線充電”治理研究

社區“飛線充電”如何治理

Cadence Allegro 17.4PCB阻抗分析功能操作說

直接下載了OPA659的PCB封裝,用ultra librarian導入到cadence allegro 16.6里面,為什么會報錯?

Cadence快板PCB培訓

Cadence攜手Intel代工廠研發先進封裝流程,助力HPC、AI及移動設備

利用Sigrity Aurora進行PCB布線后的仿真分析-阻抗及寄生參數析

?Cadence Allegro飛線的隱藏關閉

?Cadence Allegro飛線的隱藏關閉

評論