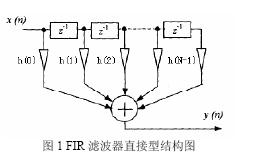

FIR濾波器公式為:

y[m] = b[0]x[m] + b[1]x[m-1] + …. + b[p]x[m-p]

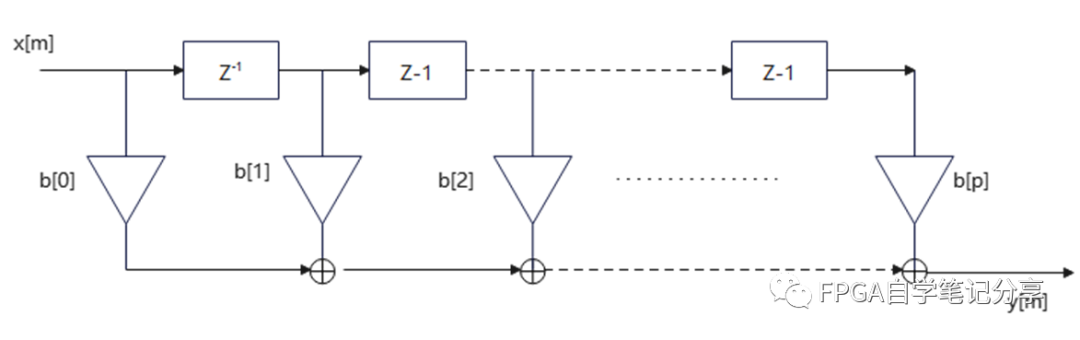

其運算結構如下:

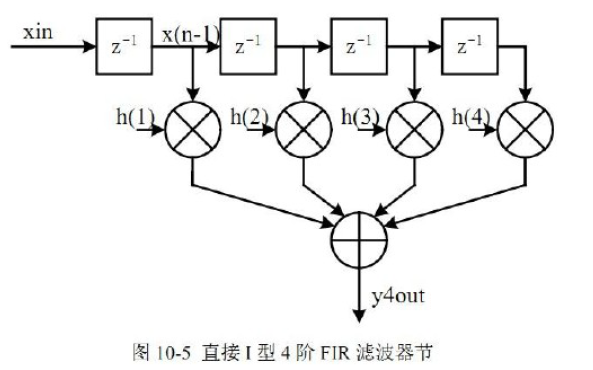

詳細的計算過程為:

可以看到需要p+1個乘法器。

在數(shù)字信號處理中為了保證時延穩(wěn)定性以及節(jié)省乘法器,通常使用對稱系數(shù)的濾波器 ,即:

b[0] = b[p] b[1]=b[p-1] …..

此時濾波器結構為:

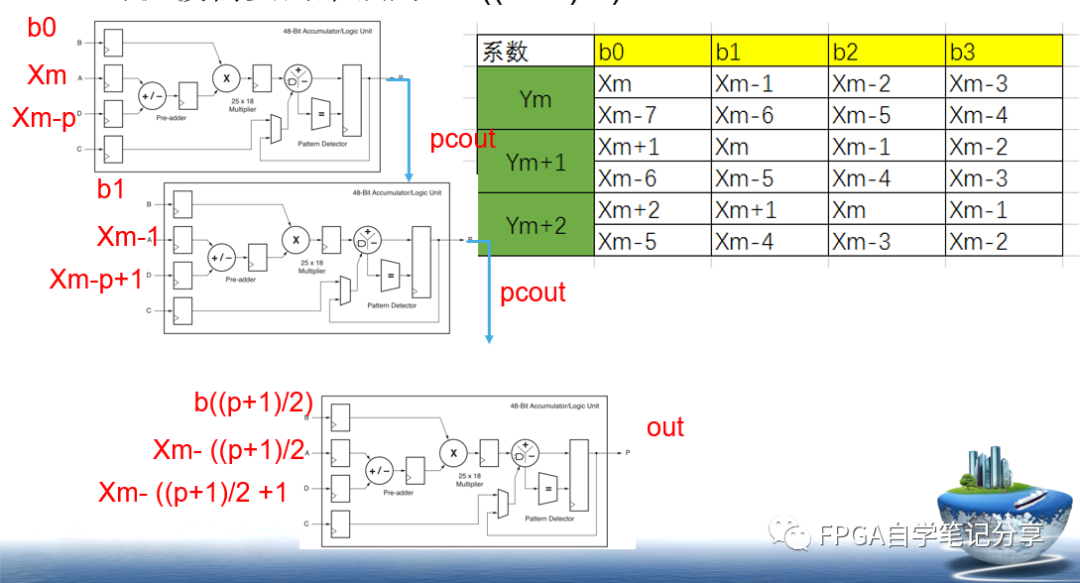

此時fir的卷積計算可以化簡為:

y[m] = b[0]x[m] + b[1]x[m-1] + …. + b[p]x[m-p]

=b[0] (x[m]+x[m-p]) + b[1] (x[m-1] + x[m-p-1]) +….

此時濾波需要的乘法為ceil((P+1)/2),可以發(fā)現(xiàn)這種結構將節(jié)省一半的乘法器。

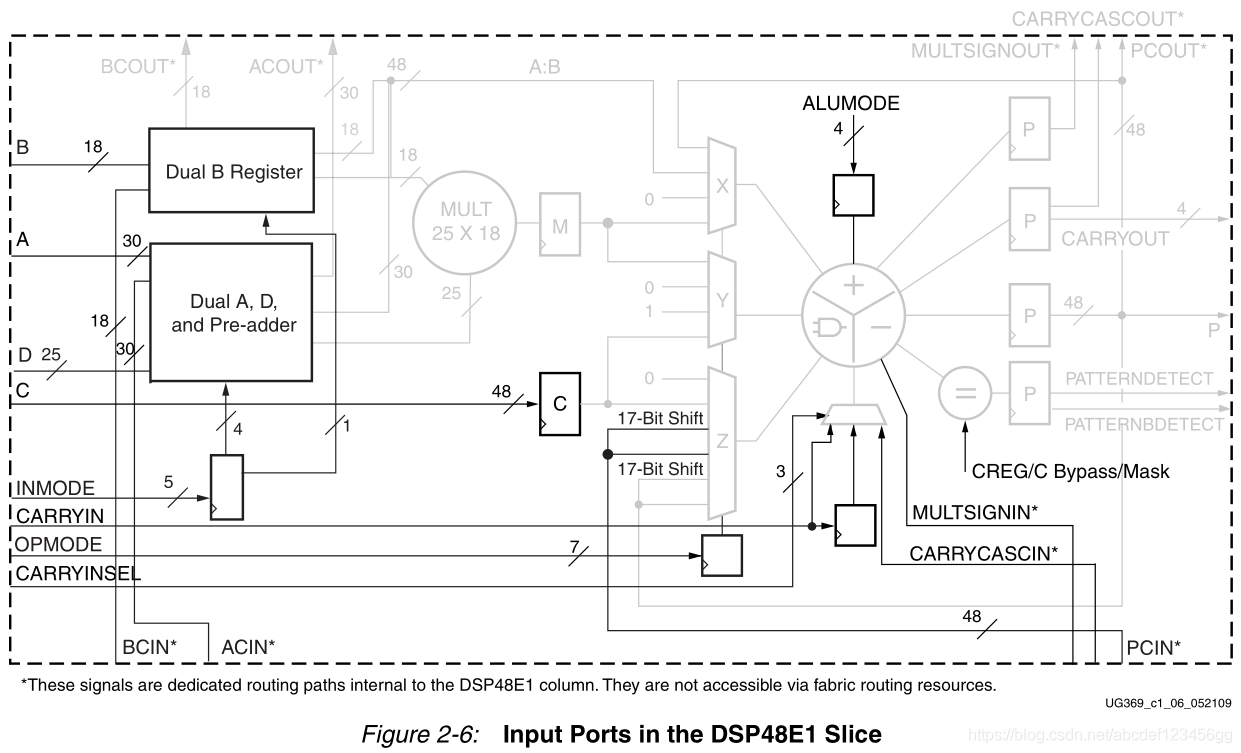

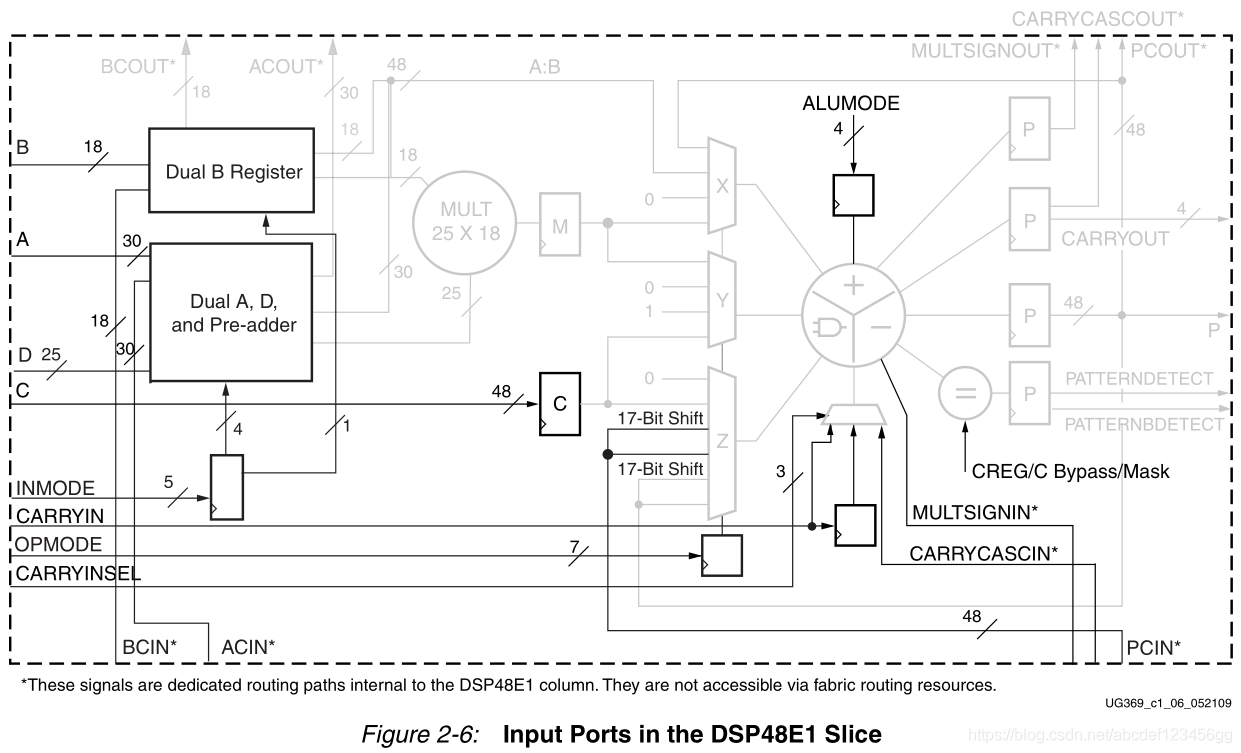

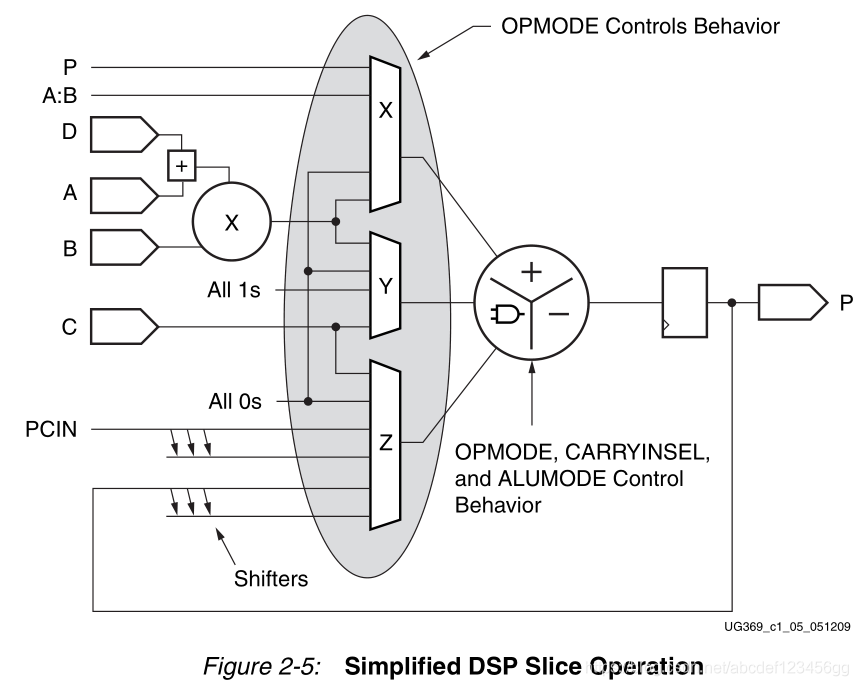

此時我們回頭看一下dsp48e1的結構(詳細可見FPGA的底層資源之DSP48E1),發(fā)現(xiàn)dsp的結構中就有預加、乘法、級聯(lián)累加(紅框所示),剛好用來實現(xiàn)對稱結構的fir濾波器。

可以得到dsp48e1實現(xiàn)fir濾波器實現(xiàn)結構為:

在回顧一下之前講dsp48e1使用的重點:

inmode使用00101,讓A、B、D三個端口對齊輸入,C延后兩個clk

opmode[3:0]使用0101,使用M作為X,Y的數(shù)據(jù);

DSP48E1使用總結:

1、 A、B、D三個端口對齊在同一時刻輸入;

2、P在數(shù)據(jù) A、B、D輸入后的第四個clk輸出;

3、C數(shù)據(jù)在數(shù)據(jù) A、B、D輸入的第二個clk輸入;

4、Pcin級聯(lián)時數(shù)據(jù)要在數(shù)據(jù) A、B、D輸入的第三個clk輸入;

5、 OPMODE,ALUMODE在數(shù)據(jù) A、B、D輸入的第二個clk輸入;

OPMODE的配置說明:

好了,dsp48e1實現(xiàn)對稱系數(shù)的fir濾波器的結構就是這個樣子了,大家可以嘗試編寫一下fir濾波器,下一篇文章上代碼和仿真。

-

濾波器

+關注

關注

161文章

7862瀏覽量

178945 -

數(shù)字信號處理

+關注

關注

15文章

563瀏覽量

46005 -

FIR

+關注

關注

4文章

147瀏覽量

33293 -

乘法器

+關注

關注

8文章

206瀏覽量

37195 -

DSP48E1

+關注

關注

0文章

5瀏覽量

625

發(fā)布評論請先 登錄

相關推薦

為什么BUFG驅(qū)動DSP48E1的CE會出現(xiàn)問題?

DSP48E1的屬性詳解

7系列FPGA DSP48E1片的特點

什么是fir數(shù)字濾波器 什么叫FIR濾波器

System generator DSP48E1 (1):端口說明

使用DSP設計和仿真FIR濾波器

DSP48E1詳解(3): DSP48E1屬性

7系列FPGA DSP48E1的參數(shù)特點概述

DSP48E1詳解(1):7系列FPGA DSP48E1片的特點

DSP48E1詳解(3):DSP48E1屬性

DSP48E1詳解(2):簡化DSP48E1片操作

基于DSP48E1的FIR濾波器設計

基于DSP48E1的FIR濾波器設計

評論