為了及時完成捷變射頻收發(fā)器設(shè)計,使用針對寬帶而優(yōu)化的高性能轉(zhuǎn)換器及其相關(guān)的高速FPGA是有必要的,但許多設(shè)計人員還需要其它資源。由于器件的復(fù)雜性,考慮到互連格式和協(xié)議的挑戰(zhàn),以及電路板布局的微妙,“獨自一人”或“幾乎獨立”地完成設(shè)計已不再可行。

傳統(tǒng)上,SDR平臺需要多種技能結(jié)合才能實現(xiàn)完整的SDR解決方案,包括RF和ADC設(shè)計、數(shù)字硬件、SOC裝配、DSP硬件和軟件開發(fā)技能。克服技能缺陷的一種辦法是利用參考設(shè)計和MatLab等支持工具來幫助完成一個有效實例。

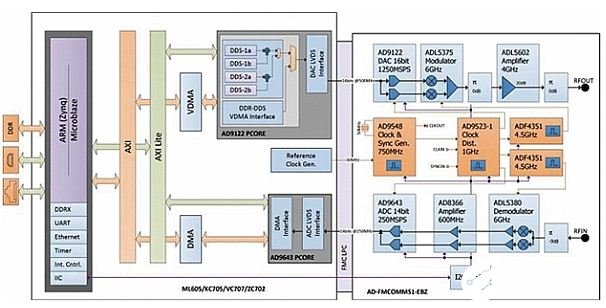

圖1:FMCOMMS1-EBZ為眾多計算密集型FPGA無線電應(yīng)用(包括SDR)提供模擬前端。與FPGA開發(fā)平臺一起使用時,F(xiàn)MCOMMS1-EBZ能夠在物理層實現(xiàn)從基帶到RF的一系列無線通信功能。

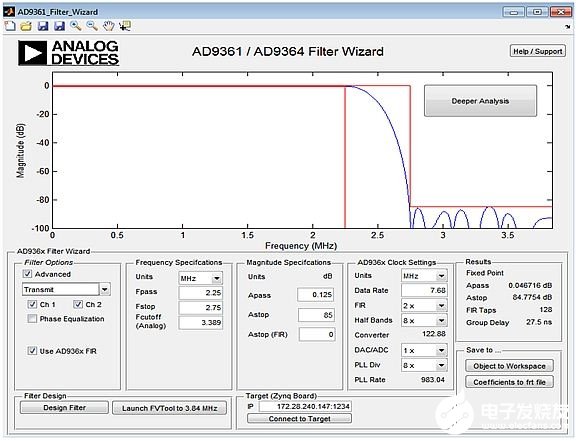

例如,一個常見的SDR挑戰(zhàn)是設(shè)計可編程濾波器。SDR平臺內(nèi)有可編程TIA濾波器、低通濾波器、數(shù)字半帶濾波器和可編程FIR濾波器。 每個濾波器都會影響器件鏈中的下一濾波器。因此,當(dāng)出現(xiàn)異常時,設(shè)計人員可能會發(fā)現(xiàn)很難確定問題所在。

圖2:ADI公司Wiki知識庫中的SDR系統(tǒng)功能框圖

利用參考設(shè)計,設(shè)計人員可以看到不同的濾波器級,了解各濾波器級如何在通帶中產(chǎn)生獨特的幅度滾降和群延遲。通過了解該獨特的幅度滾降和群延遲是如何及在哪里發(fā)生的,設(shè)計人員就能補償FIR濾波器中的延遲,進(jìn)而在數(shù)字基帶器件中實現(xiàn)平坦的通帶響應(yīng)。ADI公司wiki知識庫提供了很好的參考設(shè)計資源。

設(shè)計人員的另一個挑戰(zhàn)是如何設(shè)計FIR濾波器,使其補償之前所有級的累積影響。這里,可以利用一個濾波器設(shè)計MATLAB小應(yīng)用程序來設(shè)計發(fā)送器和接收器的FIR濾波器,幫助設(shè)計人員考慮來自濾波器鏈中其它模擬和數(shù)字濾波器級的幅度和相位響應(yīng)。

通過選用具有合適特性的器件,并輔以評估工具、應(yīng)用支持、參考設(shè)計以及第三方技術(shù)和產(chǎn)品,開發(fā)團隊將更有可能達(dá)成多個設(shè)計目標(biāo),并滿足成本和時間上的要求。

圖3:MathWorks的MATLAB可用于無線SDR系統(tǒng)和器件中的復(fù)雜濾波器設(shè)計。這里,AD-FMCOMMS2-EBZ和AD-FMCOMMS4-EBZ SDR開發(fā)平臺上集成的ADI公司AD9361和AD9364 RF收發(fā)器的模型,顯示了如何利用一個示例系統(tǒng)設(shè)計中產(chǎn)生的系數(shù)來為內(nèi)部FIR濾波器設(shè)計一個濾波器。

無論系統(tǒng)工程師喜歡使用FMC還是商用SDR平臺,借助支持工具和資源將令系統(tǒng)工程師領(lǐng)先一大步。

責(zé)任編輯:gt

-

收發(fā)器

+關(guān)注

關(guān)注

10文章

3454瀏覽量

106251 -

射頻

+關(guān)注

關(guān)注

104文章

5620瀏覽量

168230 -

SDR

+關(guān)注

關(guān)注

7文章

234瀏覽量

50581

發(fā)布評論請先 登錄

相關(guān)推薦

有關(guān)SDR平臺咨詢

軟件無線電(SDR)平臺帶你從頻譜共享到5G研發(fā)

基于AD9361的SDR商用平臺

Spartan 6是否支持SDR SDRAM?

介紹SDR的技術(shù)原理 以SDR LTE系統(tǒng)為例進(jìn)一步解析SDR系統(tǒng)的工作流程

實現(xiàn)SDR所需的開發(fā)方法有哪些

ADC技術(shù)在SDR實現(xiàn)中有哪些挑戰(zhàn)?

5G網(wǎng)絡(luò)架構(gòu),5G中的SDR和SDN是什么?

ADC技術(shù)在SDR實現(xiàn)中的挑戰(zhàn)

利用捷變收發(fā)器來簡化SDR平臺設(shè)計復(fù)雜度并提高實際運算效能

SDR的技術(shù)原理介紹及案例分析

基于DSP和賽靈思Spartan-6的SDR系統(tǒng)設(shè)計與實現(xiàn)

RF SDR設(shè)計:ADI/Xilinx SDR原型制作系統(tǒng)、工具流程資料下載

SDR平臺如何借助支持工具和資源在設(shè)計系統(tǒng)中實現(xiàn)應(yīng)用

SDR平臺如何借助支持工具和資源在設(shè)計系統(tǒng)中實現(xiàn)應(yīng)用

評論