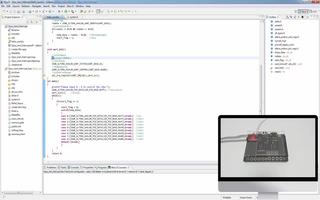

軟核演練篇包含了哪些內(nèi)容:該篇以什么是軟核、什么是Qsys、如何構(gòu)建一個Qsys系統(tǒng)為切入點,在該基礎(chǔ)上進一步介紹了Nios II處理器的體系結(jié)構(gòu)、Qsys豐富多彩的內(nèi)置IP,以及Avalon總線接口規(guī)范,然后又以Avalon總線接口規(guī)范為基礎(chǔ),進一步定制了開發(fā)板所有外設(shè)的IP核。最后,又以系統(tǒng)uC/OS-II和uCGUI為例進行了應(yīng)用開發(fā)的介紹。本篇不同于傳統(tǒng)的傻瓜式教程,將理論和實踐相結(jié)合,不僅僅講述了怎樣做,更進一步講述了為什么要這樣做。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21798瀏覽量

606051 -

NIOSII

+關(guān)注

關(guān)注

0文章

59瀏覽量

28024 -

IP核

+關(guān)注

關(guān)注

4文章

331瀏覽量

49644

發(fā)布評論請先 登錄

相關(guān)推薦

FPGA之軟核演練篇:內(nèi)置IP核之UART的應(yīng)用實戰(zhàn)講解-中斷

FPGA之軟件工具篇:PLL IP核的使用講解

FPGA之軟核演練篇:內(nèi)置IP核之Interval Timer的理論原理講解

FPGA之軟核演練篇:內(nèi)置IP核之PIO的實戰(zhàn)應(yīng)用講解

FPGA之軟核演練篇:內(nèi)置IP核之EPCS的理論實戰(zhàn)講解

鋯石FPGA A4_Nano開發(fā)板視頻:內(nèi)置IP核之Interval Timer的應(yīng)用實戰(zhàn)講解

鋯石FPGA A4_Nano開發(fā)板視頻:內(nèi)置IP核之Interval Timer的理論原理講解

FPGA之軟核演練篇:內(nèi)置IP核之Interval Timer的應(yīng)用實戰(zhàn)講解

FPGA之軟核演練篇:內(nèi)置IP核之Interval Timer的應(yīng)用實戰(zhàn)講解

評論